雖然這篇architecture電腦鄉民發文沒有被收入到精華區:在architecture電腦這個話題中,我們另外找到其它相關的精選爆讚文章

在 architecture電腦產品中有41篇Facebook貼文,粉絲數超過180萬的網紅中時新聞網,也在其Facebook貼文中提到, 世代轉換來了! #英特爾 #晶片 #電腦 #科技 #INTEL...

同時也有166部Youtube影片,追蹤數超過531的網紅Humans Offshore Podcast離島人,也在其Youtube影片中提到,Ep052 -建築設計、數位製造與電腦科學的跨領域研究:高鼎鈞⠀ 這週邀請到建築設計、數位製造與電腦科學的跨領域研究:高鼎鈞學長⠀ 學長從淡江大學建築系畢業後,在陳珍誠教授的研究室的研究與教學助理⠀ 碩士則到斯圖加特大學的計算機設計學院與建築與結構設計學院進行研究⠀ 畢業後在當地營建工程公司的建築...

「architecture電腦」的推薦目錄

- 關於architecture電腦 在 Amau Yang ️ Instagram 的最佳貼文

- 關於architecture電腦 在 ʜᴀɴᴅʙʟᴇ | ᴘʜᴏᴛᴏɢʀᴀᴘʜʏ Instagram 的最佳貼文

- 關於architecture電腦 在 國立臺灣科學教育館 Instagram 的最佳貼文

- 關於architecture電腦 在 中時新聞網 Facebook 的精選貼文

- 關於architecture電腦 在 台灣物聯網實驗室 IOT Labs Facebook 的精選貼文

- 關於architecture電腦 在 眼底城事 eyes on place Facebook 的精選貼文

- 關於architecture電腦 在 Humans Offshore Podcast離島人 Youtube 的最佳解答

- 關於architecture電腦 在 Humans Offshore Podcast離島人 Youtube 的最讚貼文

- 關於architecture電腦 在 鍾日欣 Youtube 的最佳解答

architecture電腦 在 Amau Yang ️ Instagram 的最佳貼文

2021-05-01 18:51:43

忙了整個四月 趁著哥哥的生涯大事 全家人一起去了趟宜蘭旅行 回程途中也順路去把工作室簽約 找了一個多月看了無數間房子 好不容易等到了適合我們的空間 再來還要一段時間來室內裝潢 一步一步也慢慢走向目標中理想的樣貌 但這一切也真的很辛苦 所謂的自由工作者也常常被誤會 看似沒有被公司上下班時間拘束 不...

architecture電腦 在 ʜᴀɴᴅʙʟᴇ | ᴘʜᴏᴛᴏɢʀᴀᴘʜʏ Instagram 的最佳貼文

2021-03-31 18:04:22

Architecture geometry . 此次很榮幸能和 @gastonluga 合作,簡約的設計又不缺乏機能上的配置,防水的材質適合在台北宜蘭的天氣,如果最近想找城市電腦包是個不錯的選擇! . 官網訂購輸入專屬優惠碼【Handble】即享8.5折優惠。 https://gastonluga...

architecture電腦 在 國立臺灣科學教育館 Instagram 的最佳貼文

2021-08-03 14:57:49

愛因斯坦說:「想像力比知識重要」 二十世紀初真空管的發明,使得收音機、長途電話、無線電報、雷達、電腦相繼發展,但真空管體積大又耗電,促使美國貝爾實驗室於二戰期間成功研製一種體積很小,卻可以代替真空管的「電晶體」。 半導體電子元件的大小從毫米、微米進化到奈米等級,體積雖然越來越小其功能卻越來越強大...

-

architecture電腦 在 Humans Offshore Podcast離島人 Youtube 的最佳解答

2020-10-19 08:00:06Ep052 -建築設計、數位製造與電腦科學的跨領域研究:高鼎鈞⠀

這週邀請到建築設計、數位製造與電腦科學的跨領域研究:高鼎鈞學長⠀

學長從淡江大學建築系畢業後,在陳珍誠教授的研究室的研究與教學助理⠀

碩士則到斯圖加特大學的計算機設計學院與建築與結構設計學院進行研究⠀

畢業後在當地營建工程公司的建築資訊研究部門、擔任程式工程師與專案工程師參與研究案與開發案⠀

.⠀

目前是蘇黎世聯邦理工學院及和瑞士國家能力研究中心數位製造的博士研究員⠀

博士主要在蘇黎世聯邦理工學院建築與科技學院攻讀「建築與結構設計Architecture and Structural Design」,「數位製造Digital Fabrication」,「電腦運算設計Computational Design」,並同時在資工系輔修「電腦科學Computer Science」⠀

.⠀

⠀

透過這個機會,想跟學長請教一路上從建築開始、參與德國的營建工程、到現在在ETH黎世聯邦理工學院做跨領域研究的轉折和契機⠀

同時也想知道學長在號稱歐陸第一名校蘇黎世聯邦理工學院(ETH)的環境氛圍⠀

以及瑞士,德國與台灣唸書與工作環境的差異⠀

.⠀

若大家對高鼎鈞學長的經歷有興趣,歡迎參考學長的個人網站、Linkedin和學長聯絡交流⠀

https://www.linkedin.com/in/kaogene/⠀

https://www.geneatcg.com/⠀

.⠀

#ETH⠀

#蘇黎世聯邦理工學院⠀

#參數設計⠀

#數位製造⠀

#高鼎鈞⠀

.⠀

經歷:⠀

- 瑞士 蘇黎世聯邦理工學院(ETH Zurich) Block Research Group (Architecture and Structure) 和瑞士國家能力研究中心的數位製造領域(NCCR Digital Fabrication):博士研究員,主攻建築與結構設計,以及數位製造,電腦運算設計 。⠀

- 瑞士 ETH Zurich資工系輔修電腦科學(CAS in Computer Science)主攻視覺運算(Visual Computing)領域⠀

- 德國 德國與奧地利營建工程公司 Ed. Züblin AG / Strabag AG:程式工程師與專案工程師參與研究案與開發案⠀

- 德國 斯圖加特大學 運算設計與製造研究所(ICD)與建築與結構設計研究所(ITKE):ITECH碩士研究小組⠀

- 台灣 淡江大學 數位設計與製造實驗室:研究與教學助理⠀

- 台灣 淡江大學 建築系:學業特別與傑出設計獎⠀

⠀

🔥🔥🔥備註🔥🔥🔥⠀

✳️Block Research Group - http://www.block.arch.ethz.ch/brg/⠀

✳️NCCR Digital Fabrication - http://www.dfab.ch/⠀

✳️CAS in Computer Science - https://inf.ethz.ch/continuing-education/certificate-program.html⠀

✳️Ed. Züblin AG - https://www.zueblin.de/databases/internet/_public/content30.nsf/web30?Openagent&id=EN-ZUEBLIN.DEN_welcome.html ⠀

✳️Strabag AG - https://www.strabag.com/⠀

✳️運算設計與製造研究所(ICD) - https://icd.uni-stuttgart.de/⠀

✳️建築與結構設計研究所(ITKE) - https://www.itke.uni-stuttgart.de/de/⠀

✳️ITECH碩士研究小組 - https://icd.uni-stuttgart.de/?p=6111⠀

✳️淡江大學 數位設計與製造實驗室 - https://www.facebook.com/digitalaieou/⠀

-------------

🎧離島人們的經驗交流播客平台

A podcast platform, shares experiences of those who are offshore.

🏠 離島人Homepage | https://www.humansoffshore.com

🎬 Youtube | https://bit.ly/ho_youtube

🌹 Paypal小額贊助 | http://bit.ly/humansoffshore_paypal -

architecture電腦 在 Humans Offshore Podcast離島人 Youtube 的最讚貼文

2020-06-28 18:37:23🔥回收既有材料可以帶給數位製造什麼樣的可能性呢?

今天離島人邀請到新興材料與數位製造:吳宗儒

2012年從逢甲建築系畢業後、學長先後在廖偉立建築師事務所以及王銘鴻建築師事務所擔任建築設計師,一邊工作一邊準備作品集和語言的檢定。而在2017年學長前往瑞士ETH攻讀碩士、研究電腦運算及增材製造在建築運用上的可能性。

吳宗儒學長目前在荷蘭 The New Raw擔任Senior Architect並同時兼任瑞士World-Architects.com的Content Manager of WeChat。之前離島人節目也有邀請許多建築背景、現在在數位製造領域活躍的學長姐。包含Ep10水泥列印的吳岱宣學長、Ep40在台灣作為傳產和數位製造橋樑的施以竹學姊、Ep052在瑞士做數位製造跨領域研究的高鼎鈞學長等。

吳宗儒學長在發展的雖然也是數位製造,但是完全不同的方向。今天和宗儒學長聊聊瑞士和荷蘭對於數位製造氛圍的差異以及當數位製造面對學術之外的商業環境又有什麼樣的可能性。

歡迎大家來聽聽這週的離島人播客節目,

來聽聽 吳宗儒學長在新興材料與數位製造的經驗和分享

若大家對吳宗儒學長的經歷有興趣,歡迎參考下方學長的個人網站、LinkedIn和宗儒學長聯絡交流

🔗 https://www.linkedin.com/in/zongru-wu-62a784170/

⚠️備註

️MAS ETH DFAB▶︎▶︎ https://www.masdfab.com/

️THE NEW RAW▶︎▶︎ https://thenewraw.org/

️World-Architects.com▶︎▶︎ https://www.world-architects.com/en

️Wang Architects & Associates▶︎▶︎ http://www.waa.com.tw/en/

️AMBi-Studio▶︎▶︎ http://www.ambi.com.tw/

-----

🎙Ep083- 新興材料與數位製造:吳宗儒

#吳宗儒 #離島人 #zongru_wu #zongruwu

🏆經歷

- Jan 2019-Present

荷蘭 Senior Architect, THE NEW RAW, The Netherlands

- Jun 2018-Present

瑞士 World-Architects.com-Content Manager of WeChat, Switzerland

- Mar 2016-Aug 2017

台灣 Junior Architect, WANG Architects & Associates, Taiwan

- Feb 2014-Feb 2016

台灣 Junior Architect, AMBi-Studio, Taiwan

🎓學歷

- Sep 2017-Sep 2018

瑞士 Master of Advanced Studies in Architecture and Digital Fabrication-ETH Zurich (MAS ETH DFAB)

- Sep 2007-Jun 2013

台灣 Bachelor of Architecture Feng Chia University,

-----

🎧離島人們的經驗交流播客平台

A podcast platform, shares experiences of those who are offshore.

🎬 Youtube | https://bit.ly/ho_youtube

🎙 參與錄音 | http://bit.ly/humansoffshore_interviewform

🎧 收聽 on Spotify | http://bit.ly/podcast_humansoffshore

👉🏼 Follow us on Instagram | http://bit.ly/humansoffshore_ig

👉🏼 Follow us on Facebook | http://bit.ly/humansoffshore_fb -

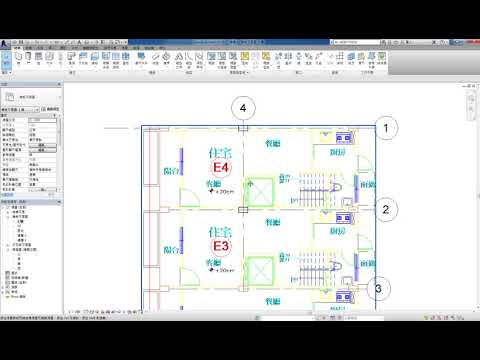

architecture電腦 在 鍾日欣 Youtube 的最佳解答

2017-09-15 23:25:51我是JC老師

電腦相關課程授課超過6000小時的一位 Revit 課程講師

由於實在太多同學向JC老師反映,希望可以有線上課程學習,所以就決定錄製一系列的 Revit 線上影片教學

而且不加密、不設限、不販售,就是純分享,希望可以幫助到有需要的朋友們

如果這部 3ds Max 教學影片對你有幫助的話,請幫我按個讚,給我點鼓勵,也多分享給需要的朋友們喔~

---------------------------------------------------------------------------------------------------------

整理CAD檔案

● 併入外部參考檔案

● 複製所需要的物件到新檔。

● 刪除不要的物件

● 炸開所有物件,直到不能炸為止

● 以一個幾準點複製到新檔的0,0

● 存檔(注意檔名)

● 所有樓層平面圖、立面圖與剖面圖都要單獨存檔

---------------------------------------------------------------------------------------------------------

匯入或連結 CAD 格式

● 開啟REVIT建築新檔

● 設定專案單位與CAD檔案單位一致

● 設定樓層高度

● 切換到正確樓層平面圖

● 開始匯入CAD檔案

● 「插入」頁籤 /「匯入」面板/ (匯入 CAD),或是按一下「插入」頁籤 /「連結」面板 / (連結 CAD)。

● 可以匯入或連結諸如 AutoCAD 2009 (DWG 和 DXF)、MicroStation® (DGN)、SketchUp (SKP 和 DWG) 以及 ACIS (SAT) 等其他 CAD 程式的向量資料。Revit Architecture 支援匯入大多數 DGN 表面和實體,但不包括圓錐、B-雲形線表面和 SmartSolid。

● 依序全部匯入

● 新建柱元件,加入柱

● 新建強元件,加入牆

● 新建門、窗、樓梯、家具….等元件並加入

---------------------------------------------------------------------------------------------------------

Revit 2016 線上教學影片目錄:http://bit.ly/2vR6fgW

Revit 2016 線上教學影片範例下載:http://bit.ly/2vR0b7X

3ds Max 2015 線上教學影片目錄:http://bitly.com/2dUGqn3

AutoCAD 2015 2D 線上教學影片目錄:http://bitly.com/2dUGm6Y

TQC AutoCAD 2008 2D 線上教學影片目錄:http://bitly.com/2dUGQtB

JC-Design網站:http://jc-d.net/

JC-Design粉絲團:https://www.facebook.com/jcdesigntw/

JC-Design LINE ID:@umd7274k

JC電子信箱:[email protected]

architecture電腦 在 中時新聞網 Facebook 的精選貼文

世代轉換來了!

#英特爾 #晶片 #電腦 #科技 #INTEL

architecture電腦 在 台灣物聯網實驗室 IOT Labs Facebook 的精選貼文

摩爾定律放緩 靠啥提升AI晶片運算力?

作者 : 黃燁鋒,EE Times China

2021-07-26

對於電子科技革命的即將終結的說法,一般認為即是指摩爾定律的終結——摩爾定律一旦無法延續,也就意味著資訊技術的整棟大樓建造都將出現停滯,那麼第三次科技革命也就正式結束了。這種聲音似乎是從十多年前就有的,但這波革命始終也沒有結束。AI技術本質上仍然是第三次科技革命的延續……

人工智慧(AI)的技術發展,被很多人形容為第四次科技革命。前三次科技革命,分別是蒸汽、電氣、資訊技術(電子科技)革命。彷彿這“第四次”有很多種說辭,比如有人說第四次科技革命是生物技術革命,還有人說是量子技術革命。但既然AI也是第四次科技革命之一的候選技術,而且作為資訊技術的組成部分,卻又獨立於資訊技術,即表示它有獨到之處。

電子科技革命的即將終結,一般認為即是指摩爾定律的終結——摩爾定律一旦無法延續,也就意味著資訊技術的整棟大樓建造都將出現停滯,那麼第三次科技革命也就正式結束了。這種聲音似乎是從十多年前就有,但這波革命始終也沒有結束。

AI技術本質上仍然是第三次科技革命的延續,它的發展也依託於幾十年來半導體科技的進步。這些年出現了不少專門的AI晶片——而且市場參與者相眾多。當某一個類別的技術發展到出現一種專門的處理器為之服務的程度,那麼這個領域自然就不可小覷,就像當年GPU出現專門為圖形運算服務一樣。

所以AI晶片被形容為CPU、GPU之後的第三大類電腦處理器。AI專用處理器的出現,很大程度上也是因為摩爾定律的發展進入緩慢期:電晶體的尺寸縮減速度,已經無法滿足需求,所以就必須有某種專用架構(DSA)出現,以快速提升晶片效率,也才有了專門的AI晶片。

另一方面,摩爾定律的延緩也成為AI晶片發展的桎梏。在摩爾定律和登納德縮放比例定律(Dennard Scaling)發展的前期,電晶體製程進步為晶片帶來了相當大的助益,那是「happy scaling down」的時代——CPU、GPU都是這個時代受益,不過Dennard Scaling早在45nm時期就失效了。

AI晶片作為第三大類處理器,在這波發展中沒有趕上happy scaling down的好時機。與此同時,AI應用對運算力的需求越來越貪婪。今年WAIC晶片論壇圓桌討論環節,燧原科技創始人暨CEO趙立東說:「現在訓練的GPT-3模型有1750億參數,接近人腦神經元數量,我以為這是最大的模型了,要千張Nvidia的GPU卡才能做。談到AI運算力需求、模型大小的問題,說最大模型超過萬億參數,又是10倍。」

英特爾(Intel)研究院副總裁、中國研究院院長宋繼強說:「前兩年用GPU訓練一個大規模的深度學習模型,其碳排放量相當於5台美式車整個生命週期產生的碳排量。」這也說明了AI運算力需求的貪婪,以及提供運算力的AI晶片不夠高效。

不過作為產業的底層驅動力,半導體製造技術仍源源不斷地為AI發展提供推力。本文將討論WAIC晶片論壇上聽到,針對這個問題的一些前瞻性解決方案——有些已經實現,有些則可能有待時代驗證。

XPU、摩爾定律和異質整合

「電腦產業中的貝爾定律,是說能效每提高1,000倍,就會衍生出一種新的運算形態。」中科院院士劉明在論壇上說,「若每瓦功耗只能支撐1KOPS的運算,當時的這種運算形態是超算;到了智慧型手機時代,能效就提高到每瓦1TOPS;未來的智慧終端我們要達到每瓦1POPS。 這對IC提出了非常高的要求,如果依然沿著CMOS這條路去走,當然可以,但會比較艱辛。」

針對性能和效率提升,除了尺寸微縮,半導體產業比較常見的思路是電晶體結構、晶片結構、材料等方面的最佳化,以及處理架構的革新。

(1)AI晶片本身其實就是對處理器架構的革新,從運算架構的層面來看,針對不同的應用方向造不同架構的處理器是常規,更專用的處理器能促成效率和性能的成倍增長,而不需要依賴於電晶體尺寸的微縮。比如GPU、神經網路處理器(NPU,即AI處理器),乃至更專用的ASIC出現,都是這類思路。

CPU、GPU、NPU、FPGA等不同類型的晶片各司其職,Intel這兩年一直在推行所謂的「XPU」策略就是用不同類型的處理器去做不同的事情,「整合起來各取所需,用組合拳會好過用一種武器去解決所有問題。」宋繼強說。Intel的晶片產品就涵蓋了幾個大類,Core CPU、Xe GPU,以及透過收購獲得的AI晶片Habana等。

另外針對不同類型的晶片,可能還有更具體的最佳化方案。如當代CPU普遍加入AVX512指令,本質上是特別針對深度學習做加強。「專用」的不一定是處理器,也可以是處理器內的某些特定單元,甚至固定功能單元,就好像GPU中加入專用的光線追蹤單元一樣,這是當代處理器普遍都在做的一件事。

(2)從電晶體、晶片結構層面來看,電晶體的尺寸現在仍然在縮減過程中,只不過縮減幅度相比過去變小了——而且為緩解電晶體性能的下降,需要有各種不同的技術來輔助尺寸變小。比如說在22nm節點之後,電晶體變為FinFET結構,在3nm之後,電晶體即將演變為Gate All Around FET結構。最終會演化為互補FET (CFET),其本質都是電晶體本身充分利用Z軸,來實現微縮性能的提升。

劉明認為,「除了基礎元件的變革,IC現在的發展還是比較多元化,包括新材料的引進、元件結構革新,也包括微影技術。長期賴以微縮的基本手段,現在也在發生巨大的變化,特別是未來3D的異質整合。這些多元技術的協同發展,都為晶片整體性能提升帶來了很好的增益。」

他並指出,「從電晶體級、到晶圓級,再到晶片堆疊、引線接合(lead bonding),精準度從毫米向奈米演進,互連密度大大提升。」從晶圓/裸晶的層面來看,則是眾所周知的朝more than moore’s law這樣的路線發展,比如把兩片裸晶疊起來。現在很熱門的chiplet技術就是比較典型的並不依賴於傳統電晶體尺寸微縮,來彈性擴展性能的方案。

台積電和Intel這兩年都在大推將不同類型的裸晶,異質整合的技術。2.5D封裝方案典型如台積電的CoWoS,Intel的EMIB,而在3D堆疊上,Intel的Core LakeField晶片就是用3D Foveros方案,將不同的裸晶疊在一起,甚至可以實現兩片運算裸晶的堆疊、互連。

之前的文章也提到過AMD剛發佈的3D V-Cache,將CPU的L3 cache裸晶疊在運算裸晶上方,將處理器的L3 cache大小增大至192MB,對儲存敏感延遲應用的性能提升。相比Intel,台積電這項技術的獨特之處在於裸晶間是以混合接合(hybrid bonding)的方式互連,而不是micro-bump,做到更小的打線間距,以及晶片之間數十倍通訊性能和效率提升。

這些方案也不直接依賴傳統的電晶體微縮方案。這裡實際上還有一個方面,即新材料的導入專家們沒有在論壇上多說,本文也略過不談。

1,000倍的性能提升

劉明談到,當電晶體微縮的空間沒有那麼大的時候,產業界傾向於採用新的策略來評價技術——「PPACt」——即Powe r(功耗)、Performance (性能)、Cost/Area-Time (成本/面積-時間)。t指的具體是time-to-market,理論上應該也屬於成本的一部分。

電晶體微縮方案失效以後,「多元化的技術變革,依然會讓IC性能得到進一步的提升。」劉明說,「根據預測,這些技術即使不再做尺寸微縮,也會讓IC的晶片性能做到500~1,000倍的提升,到2035年實現Zetta Flops的系統性能水準。且超算的發展還可以一如既往地前進;單裸晶儲存容量變得越來越大,IC依然會為產業發展提供基礎。」

500~1,000倍的預測來自DARPA,感覺有些過於樂觀。因為其中的不少技術存在比較大的邊際遞減效應,而且有更實際的工程問題待解決,比如運算裸晶疊層的散熱問題——即便業界對於這類工程問題的探討也始終在持續。

不過1,000倍的性能提升,的確說明摩爾定律的終結並不能代表第三次科技革命的終結,而且還有相當大的發展空間。尤其本文談的主要是AI晶片,而不是更具通用性的CPU。

矽光、記憶體內運算和神經型態運算

在非傳統發展路線上(以上內容都屬於半導體製造的常規思路),WAIC晶片論壇上宋繼強和劉明都提到了一些頗具代表性的技術方向(雖然這可能與他們自己的業務方向或研究方向有很大的關係)。這些技術可能尚未大規模推廣,或者仍在商業化的極早期。

(1)近記憶體運算和記憶體內運算:處理器性能和效率如今面臨的瓶頸,很大程度並不在單純的運算階段,而在資料傳輸和儲存方面——這也是共識。所以提升資料的傳輸和存取效率,可能是提升整體系統性能時,一個非常靠譜的思路。

這兩年市場上的處理器產品用「近記憶體運算」(near-memory computing)思路的,應該不在少數。所謂的近記憶體運算,就是讓儲存(如cache、memory)單元更靠近運算單元。CPU的多層cache結構(L1、L2、L3),以及電腦處理器cache、記憶體、硬碟這種多層儲存結構是常規。而「近記憶體運算」主要在於究竟有多「近」,cache記憶體有利於隱藏當代電腦架構中延遲和頻寬的局限性。

這兩年在近記憶體運算方面比較有代表性的,一是AMD——比如前文提到3D V-cache增大處理器的cache容量,還有其GPU不僅在裸晶內導入了Infinity Cache這種類似L3 cache的結構,也更早應用了HBM2記憶體方案。這些實踐都表明,儲存方面的革新的確能帶來性能的提升。

另外一個例子則是Graphcore的IPU處理器:IPU的特點之一是在裸晶內堆了相當多的cache資源,cache容量遠大於一般的GPU和AI晶片——也就避免了頻繁的訪問外部儲存資源的操作,極大提升頻寬、降低延遲和功耗。

近記憶體運算的本質仍然是馮紐曼架構(Von Neumann architecture)的延續。「在做處理的過程中,多層級的儲存結構,資料的搬運不僅僅在處理和儲存之間,還在不同的儲存層級之間。這樣頻繁的資料搬運帶來了頻寬延遲、功耗的問題。也就有了我們經常說的運算體系內的儲存牆的問題。」劉明說。

構建非馮(non-von Neumann)架構,把傳統的、以運算為中心的馮氏架構,變換一種新的運算範式。把部分運算力下推到儲存。這便是記憶體內運算(in-memory computing)的概念。

記憶體內運算的就現在看來還是比較新,也有稱其為「存算一體」。通常理解為在記憶體中嵌入演算法,儲存單元本身就有運算能力,理論上消除資料存取的延遲和功耗。記憶體內運算這個概念似乎這在資料爆炸時代格外醒目,畢竟可極大減少海量資料的移動操作。

其實記憶體內運算的概念都還沒有非常明確的定義。現階段它可能的內涵至少涉及到在儲記憶體內部,部分執行資料處理工作;主要應用於神經網路(因為非常契合神經網路的工作方式),以及這類晶片具體的工作方法上,可能更傾向於神經型態運算(neuromorphic computing)。

對於AI晶片而言,記憶體內運算的確是很好的思路。一般的GPU和AI晶片執行AI負載時,有比較頻繁的資料存取操作,這對性能和功耗都有影響。不過記憶體內運算的具體實施方案,在市場上也是五花八門,早期比較具有代表性的Mythic導入了一種矩陣乘的儲存架構,用40nm嵌入式NOR,在儲記憶體內部執行運算,不過替換掉了數位週邊電路,改用類比的方式。在陣列內部進行模擬運算。這家公司之前得到過美國國防部的資金支援。

劉明列舉了近記憶體運算和記憶體內運算兩種方案的例子。其中,近記憶體運算的這個方案應該和AMD的3D V-cache比較類似,把儲存裸晶和運算裸晶疊起來。

劉明指出,「這是我們最近的一個工作,採用hybrid bonding的技術,與矽通孔(TSV)做比較,hybrid bonding功耗是0.8pJ/bit,而TSV是4pJ/bit。延遲方面,hybrid bonding只有0.5ns,而TSV方案是3ns。」台積電在3D堆疊方面的領先優勢其實也體現在hybrid bonding混合鍵合上,前文也提到了它具備更高的互連密度和效率。

另外這套方案還將DRAM刷新頻率提高了一倍,從64ms提高至128ms,以降低功耗。「應對刷新率變慢出現拖尾bit,我們引入RRAM TCAM索引這些tail bits」劉明說。

記憶體內運算方面,「傳統運算是用布林邏輯,一個4位元的乘法需要用到幾百個電晶體,這個過程中需要進行資料來回的移動。記憶體內運算是利用單一元件的歐姆定律來完成一次乘法,然後利用基爾霍夫定律完成列的累加。」劉明表示,「這對於今天深度學習的矩陣乘非常有利。它是原位的運算和儲存,沒有資料搬運。」這是記憶體內運算的常規思路。

「無論是基於SRAM,還是基於新型記憶體,相比近記憶體運算都有明顯優勢,」劉明認為。下圖是記憶體內運算和近記憶體運算,精準度、能效等方面的對比,記憶體內運算架構對於低精準度運算有價值。

下圖則總結了業內主要的一些記憶體內運算研究,在精確度和能效方面的對應關係。劉明表示,「需要高精確度、高運算力的情況下,近記憶體運算目前還是有優勢。不過記憶體內運算是更新的技術,這幾年的進步也非常快。」

去年阿里達摩院發佈2020年十大科技趨勢中,有一個就是存算一體突破AI算力瓶頸。不過記憶體內運算面臨的商用挑戰也一點都不小。記憶體內運算的通常思路都是類比電路的運算方式,這對記憶體、運算單元設計都需要做工程上的考量。與此同時這樣的晶片究竟由誰來造也是個問題:是記憶體廠商,還是數文書處理器廠商?(三星推過記憶體內運算晶片,三星、Intel垂直整合型企業似乎很適合做記憶體內運算…)

(2)神經型態運算:神經型態運算和記憶體內運算一樣,也是新興技術的熱門話題,這項技術有時也叫作compute in memory,可以認為它是記憶體內運算的某種發展方向。神經型態和一般神經網路AI晶片的差異是,這種結構更偏「類人腦」。

進行神經型態研究的企業現在也逐漸變得多起來,劉明也提到了AI晶片「最終的理想是在結構層次模仿腦,元件層次逼近腦,功能層次超越人腦」的「類腦運算」。Intel是比較早關注神經型態運算研究的企業之一。

傳說中的Intel Loihi就是比較典型存算一體的架構,「這片裸晶裡面包含128個小核心,每個核心用於模擬1,024個神經元的運算結構。」宋繼強說,「這樣一塊晶片大概可以類比13萬個神經元。我們做到的是把768個晶片再連起來,構成接近1億神經元的系統,讓學術界的夥伴去試用。」

「它和深度學習加速器相比,沒有任何浮點運算——就像人腦裡面沒有乘加器。所以其學習和訓練方法是採用一種名為spike neutral network的路線,功耗很低,也可以訓練出做視覺辨識、語言辨識和其他種類的模型。」宋繼強認為,不採用同步時脈,「刺激的時候就是一個非同步電動勢,只有工作部分耗電,功耗是現在深度學習加速晶片的千分之一。」

「而且未來我們可以對不同區域做劃分,比如這兒是視覺區、那兒是語言區、那兒是觸覺區,同時進行多模態訓練,互相之間產生關聯。這是現在的深度學習模型無法比擬的。」宋繼強說。這種神經型態運算晶片,似乎也是Intel在XPU方向上探索不同架構運算的方向之一。

(2)微型化矽光:這個技術方向可能在層級上更偏高了一些,不再晶片架構層級,不過仍然值得一提。去年Intel在Labs Day上特別談到了自己在矽光(Silicon Photonics)的一些技術進展。其實矽光技術在連接資料中心的交換機方面,已有應用了,發出資料時,連接埠處會有個收發器把電訊號轉為光訊號,透過光纖來傳輸資料,另一端光訊號再轉為電訊號。不過傳統的光收發器成本都比較高,內部元件數量大,尺寸也就比較大。

Intel在整合化的矽光(IIIV族monolithic的光學整合化方案)方面應該是商業化走在比較前列的,就是把光和電子相關的組成部分高度整合到晶片上,用IC製造技術。未來的光通訊不只是資料中心機架到機架之間,也可以下沉到板級——就跟現在傳統的電I/O一樣。電互連的主要問題是功耗太大,也就是所謂的I/O功耗牆,這是這類微型化矽光元件存在的重要價值。

這其中存在的技術挑戰還是比較多,如做資料的光訊號調變的調變器調變器,據說Intel的技術使其實現了1,000倍的縮小;還有在接收端需要有個探測器(detector)轉換光訊號,用所謂的全矽微環(micro-ring)結構,實現矽對光的檢測能力;波分複用技術實現頻寬倍增,以及把矽光和CMOS晶片做整合等。

Intel認為,把矽光模組與運算資源整合,就能打破必須帶更多I/O接腳做更大尺寸處理器的這種趨勢。矽光能夠實現的是更低的功耗、更大的頻寬、更小的接腳數量和尺寸。在跨處理器、跨伺服器節點之間的資料互動上,這類技術還是頗具前景,Intel此前說目標是實現每根光纖1Tbps的速率,並且能效在1pJ/bit,最遠距離1km,這在非本地傳輸上是很理想的數字。

還有軟體…

除了AI晶片本身,從整個生態的角度,包括AI感知到運算的整個鏈條上的其他組成部分,都有促成性能和效率提升的餘地。比如這兩年Nvidia從軟體層面,針對AI運算的中間層、庫做了大量最佳化。相同的底層硬體,透過軟體最佳化就能實現幾倍的性能提升。

宋繼強說,「我們發現軟體最佳化與否,在同一個硬體上可以達到百倍的性能差距。」這其中的餘量還是比較大。

在AI開發生態上,雖然Nvidia是最具發言權的;但從戰略角度來看,像Intel這種研發CPU、GPU、FPGA、ASIC,甚至還有神經型態運算處理器的企業而言,不同處理器統一開發生態可能更具前瞻性。Intel有個稱oneAPI的軟體平台,用一套API實現不同硬體性能埠的對接。這類策略對廠商的軟體框架構建能力是非常大的考驗——也極大程度關乎底層晶片的執行效率。

在摩爾定律放緩、電晶體尺寸微縮變慢甚至不縮小的前提下,處理器架構革新、異質整合與2.5D/3D封裝技術依然可以達成1,000倍的性能提升;而一些新的技術方向,包括近記憶體運算、記憶體內運算和微型矽光,能夠在資料訪存、傳輸方面產生新的價值;神經型態運算這種類腦運算方式,是實現AI運算的目標;軟體層面的最佳化,也能夠帶動AI性能的成倍增長。所以即便摩爾定律嚴重放緩,AI晶片的性能、效率提升在上面提到的這麼多方案加持下,終將在未來很長一段時間內持續飛越。這第三(四)次科技革命恐怕還很難停歇。

資料來源:https://www.eettaiwan.com/20210726nt61-ai-computing/?fbclid=IwAR3BaorLm9rL2s1ff6cNkL6Z7dK8Q96XulQPzuMQ_Yky9H_EmLsBpjBOsWg

architecture電腦 在 眼底城事 eyes on place Facebook 的精選貼文

▌社群媒體時代的 #景觀設計 ▌應該回歸 #場所營造 的核心價值

數位媒體徹底了改變了規劃設計專業的執業環境。社群媒體效應也的確能夠為城市、商業的宣傳與收益帶來直接的效果,也是一個能夠有效傳達政績的途徑。但是一些規劃設計卻開始單純以成為「網紅」設計為目的,旅遊目的地被視為單純的「打卡點」,原本應該專注在「場所營造」的規劃設計,卻偏重在沒有生命的「場景」營造。

作者注意到專業者開始崇尚「網紅」的設計,但規劃設計作為一個以創造空間環境為本的專業,需要體認屏幕之外的真實空間、生活體驗,才應該是營造雋永、恆久空間的基礎。

本文整理了筆者對當下網紅設計現象的觀察,期待藉由分析受社群媒體衝擊下的專業環境,以討論社群媒體時代的設計創新課題。作者根據近年來在執業中的觀察,提出了三個針對專業環境的分析。

(1) 設計過程的速食化:更為多元、圖像化,但片段的設計資訊帶來了速食的設計過程

(2) 社群媒體的雙向、互動機制促使規劃設計者更為直接的評估設計成果與面對大眾的檢視,規劃設計者變得比以往更為直接的面對大眾的檢視,設計成果評估也變得更為直接

( 3) 專業的社群媒體中所呈現出來的內容直接反映了代表的族群以及其獲利模式,卻未必代表了內容的專業價值。網路聲量大的設計作品與規劃設計機構也未必就是好的設計與團隊。加上氾濫的媒體傳播,造成了混淆、似是而非的專業價值觀。

深刻而永續的旅遊地點創造需要完整的規劃與整體的景觀配合,場所營造需要的真實的生活、文化的融入。相反的,「網紅點」的創造卻只需要滿足佈景般、能夠置入電腦與手機屏幕大小的場景,為了突出佈景的效果,絢爛的色彩、突兀的造型、博人注意的主題。

原文刊於 中華民國景觀學會《景觀》雜誌2020年第二期。

https://eyesonplace.net/2021/04/15/16811/